Energy Research and Development Division FINAL PROJECT REPORT

# Mobile Efficiency for Plug-Load Devices

Developing a Portfolio of Advanced Efficiency Solutions: Plug-Load Technologies and Approaches for Buildings -Phase II

**California Energy Commission**

Gavin Newsom, Governor

April 2019 | CEC-500-2019-044

#### PREPARED BY:

#### **Primary Author(s)**:

Davorin Mista Yefu Wang, Ph.D. Joshua Kuhlmann Vojin Zivojnovic, Ph.D.

AGGIOS, Inc 5251 California Ave Irvine, CA 92673 Phone: 949-212-0130 | Fax: 949-212-0130 http://www.aggios.com

Contract Number: EPC-15-021

**PREPARED FOR:** California Energy Commission

Felix Villanueva Project Manager

Virginia Lew Office Manager ENERGY EFFICIENCY RESEARCH OFFICE

Laurie ten Hope Deputy Director ENERGY RESEARCH AND DEVELOPMENT DIVISION

Drew Bohan Executive Director

#### DISCLAIMER

This report was prepared as the result of work sponsored by the California Energy Commission. It does not necessarily represent the views of the Energy Commission, its employees or the State of California. The Energy Commission, the State of California, its employees, contractors and subcontractors make no warranty, express or implied, and assume no legal liability for the information in this report; nor does any party represent that the uses of this information will not infringe upon privately owned rights. This report has not been approved or disapproved by the California Energy Commission nor has the California Energy Commission passed upon the accuracy or adequacy of the information in this report.

# ACKNOWLEDGEMENTS

The authors acknowledge the vision, determination, and support of the California Energy Commission that initiated, motivated, guided, and funded the research in the efficiency of plugload devices presented here.

# PREFACE

The California Energy Commission's Energy Research and Development Division supports energy research and development programs to spur innovation in energy efficiency, renewable energy and advanced clean generation, energy-related environmental protection, energy transmission and distribution and transportation.

In 2012, the Electric Program Investment Charge (EPIC) was established by the California Public Utilities Commission to fund public investments in research to create and advance new energy solution, foster regional innovation, and bring ideas from the lab to the marketplace. The California Energy Commission and the state's three largest investor-owned utilities—Pacific Gas and Electric Company, San Diego Gas & Electric Company, and Southern California Edison Company—were selected to administer the EPIC funds and advance novel technologies, tools, and strategies that benefit their electric ratepayers.

The Energy Commission is committed to ensuring public participation in its research and development programs that promote greater reliability, lower costs, and increase safety for the California electric ratepayer and include:

- Providing societal benefits.

- Reducing greenhouse gas emission in the electricity sector at the lowest possible cost.

- Supporting California's loading order to meet energy needs first with energy efficiency and demand response, next with renewable energy (distributed generation and utility scale), and, finally, with clean, conventional electricity supply.

- Supporting low-emission vehicles and transportation.

- Providing economic development.

- Using ratepayer funds efficiently.

*Mobile Efficiency for Plug-Load Devices* is the final report of the project Developing a Portfolio of Advanced Efficiency Solutions: Plug-Load Technologies and Approaches for Buildings (Contract Number EPC-15-021) The information from this project contributes to Energy Research and Development Division's EPIC Program.

All figures and tables are the work of the author(s) for this project unless otherwise cited or credited.

For more information about the Energy Research and Development Division, please visit the Energy Commission's website at <u>www.energy.ca.gov/research/</u> or contact the Energy Commission at 916-327-1551.

# ABSTRACT

Why do mobile devices, like smart phones, use significantly less energy than plugged devices, like computers, while offering comparable functionality to users? This question naturally arises as users of mobile devices experience undistinguishable web browsing, video streaming, and other services from their battery-operated mobile devices. Can researchers learn from the design principles for mobile devices in order to close the mobile energy gap and save energy consumption for billions of plug-load devices?

Design principles define the technical steps engineers take to create new devices. The legacy design principle for plug-load devices is to focus on functionality and performance first and deal with energy efficiency later once the device is fully developed. This legacy principle results in vastly suboptimal energy efficiency of devices. Only the largest and most profitable mobile businesses, like Apple<sup>®</sup>, have been able to overcome this legacy and consistently follow energy-efficient design principles.

This project aims to save energy by applying the mobile design principles to plug loads and delivering four design principles for energy-efficient development of plug-load devices. These are the methodology document, technical standard, virtual prototype, and real-life reference design. With these principles, any engineers properly skilled in the design and production of standard electronic devices can assess the opportunities for energy savings.

Consistent use of the new technology can reduce the annual energy consumption of targeted home and business electronic plug-load devices in California's homes and offices by 20-50 percent and achieve statewide cumulative savings through 2022 of 1.6–4 terawatt-hours, depending on the range of addressable products and depth of per unit savings. (A terawatt is a trillion watts.)

**Keywords:** Energy efficiency, plug-load devices, miscellaneous electrical loads (MEL), unified hardware abstraction, software defined energy management

Please use the following citation for this report:

Author(s) Mista, Davorin, Yefu, Wang, Ph.D., Joshua, Kuhlman, Vojin, Zivojnovic, Ph.D. 2019. *Mobile efficiency for Plug-Load Devices*. California Energy Commission. Publication Number: CEC-500-2019-044.

# TABLE OF CONTENTS

|                                               | Page |

|-----------------------------------------------|------|

| ACKNOWLEDGEMENTS                              | i    |

| PREFACE                                       | ii   |

| ABSTRACT                                      | iii  |

| TABLE OF CONTENTS                             | iv   |

| LIST OF FIGURES                               | vi   |

| LIST OF TABLES                                | viii |

| EXECUTIVE SUMMARY                             |      |

| Introduction                                  | 1    |

| Project Purpose                               |      |

| Project Process                               |      |

| Project Results                               |      |

| Benefits to California                        | 4    |

| CHAPTER 1: Overview                           |      |

| CHAPTER 2: Methodology                        | 6    |

| Energy-First Development Process              | 6    |

| Power Modeling using UHA                      | 6    |

| UHA Language Elements                         | 6    |

| Modeling Hardware Components and Power States |      |

| Modeling Software and External Events         | 8    |

| Modeling Dependencies                         | 8    |

| Modeling Latencies                            | 9    |

| Power Accounting in UHA                       |      |

| Optimizing Energy Efficiency on the Device    |      |

| Power Measurements                            |      |

| Software Defined Energy Management            |      |

| EEMI Interface                                |      |

| Overview                                      |      |

| Use Cases                                     |      |

| Optimized Power Management Firmware           |      |

| CHAPTER 3: Virtual Prototypes                  |    |

|------------------------------------------------|----|

| High-Level Modeling                            |    |

| Set-Top-Box High-Level Modeling                |    |

| PC High-Level Modeling                         |    |

| TV High-Level Modeling                         |    |

| Gaming Console High-Level Modeling             |    |

| Subsystem Energy Modeling                      |    |

| Modeling Techniques                            |    |

| Power Models of Components                     |    |

| Latency Modeling                               |    |

| Latency Modeling Based on Datasheet            |    |

| Latency Modeling from Logging Timestamps       |    |

| User Behavior Modeling                         |    |

| Device Usage Patterns                          |    |

| Environment Impact Patterns                    |    |

| Simulation Results                             |    |

| TV Virtual Prototype                           |    |

| Computer Virtual Prototype                     |    |

| Set-Top-Box Virtual Prototype                  |    |

| Gaming Console Virtual Prototype               |    |

| CHAPTER 4: Reference Designs                   |    |

| Components Implementation                      |    |

| Hardware platform                              |    |

| Operating system and application software      |    |

| Testbed                                        |    |

| Hardware Tools                                 |    |

| Software Tools for per-rail power measurements |    |

| Test Plan                                      |    |

| Measurements and Power Saving Analysis         | 75 |

| Latency Results                                | 75 |

| TV reference design power analysis             |    |

| Computer reference design power analysis       |    |

| Set-top-box reference design power analysis    |     |

|------------------------------------------------|-----|

| Gaming console reference design power analysis |     |

| Summary of reference designs                   |     |

| CHAPTER 5: Conclusions                         |     |

| Further Work and Next Steps                    |     |

| CHAPTER 5: Technology Transfer                 |     |

| Standardization Efforts                        |     |

| Proliferation Efforts                          |     |

| REFERENCES                                     |     |

| APPENDIX A: UHA Reference Manual               | A-1 |

| APPENDIX B: UHA Modeling Guide                 | B-1 |

# LIST OF FIGURES

| Page                                                                                                  |

|-------------------------------------------------------------------------------------------------------|

| Figure 1: UHA Objects and Properties7                                                                 |

| Figure 2: Power Accounting in UHA Models11                                                            |

| Figure 3: UML Diagram for Shared Memory Use Case14                                                    |

| Figure 4: A Table Listing Typical Power Consumption Values From a USB Controller IC (Microchip, 2017) |

| Figure 5: Power Model of N25Q128A25                                                                   |

| Figure 6: USB Host Setup                                                                              |

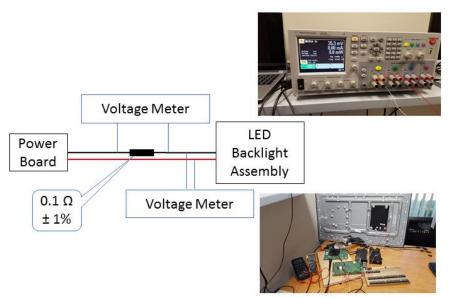

| Figure 7: Measurement Setup for Building the Power Model of the LED Backlight                         |

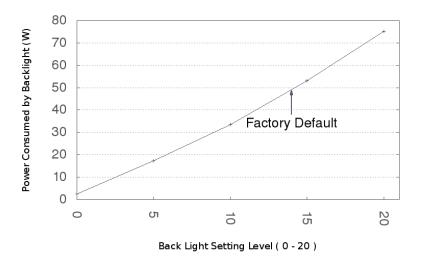

| Figure 8: Back Light Power Model                                                                      |

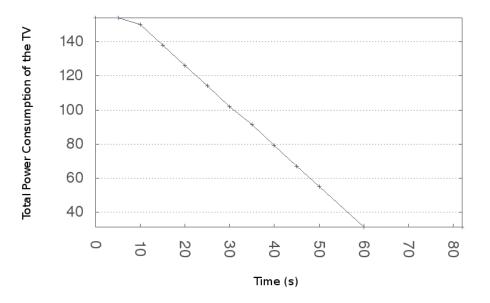

| Figure 9: TV Power Drops After a Sudden Move to a Completely Dark Environment                         |

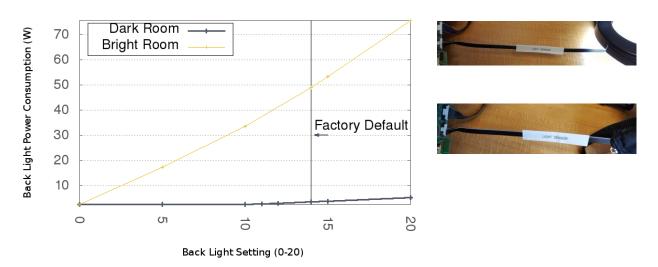

| Figure 10: Back Light Power Consumption in Dark or Bright Rooms                                       |

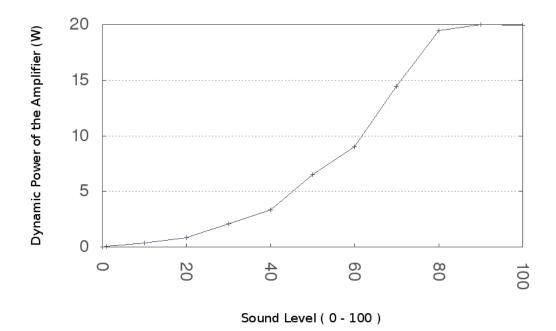

| Figure 11: Power Model of the Amplifier                                                               |

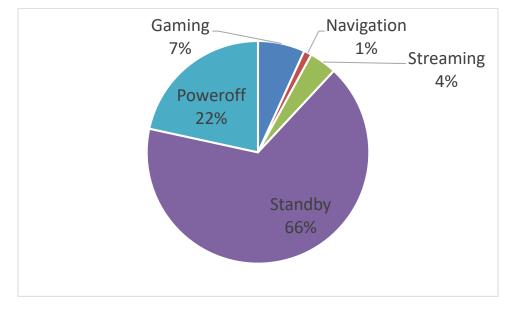

| Figure 12: Gaming Console Usage Distribution Used in Virtual Prototyping45                            |

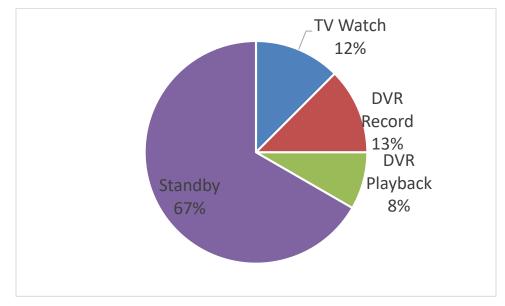

| Figure 13: Use Distribution in Set-Top Box Virtual Prototype46                                        |

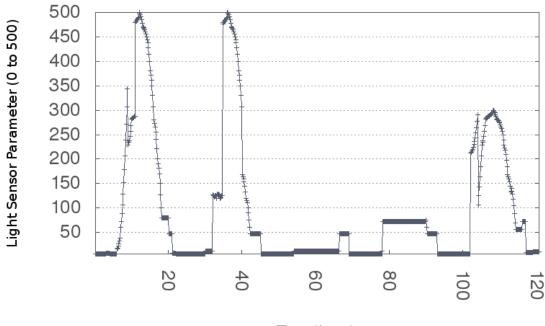

| Figure 14: Modeling Ambient Light Levels                                                              |

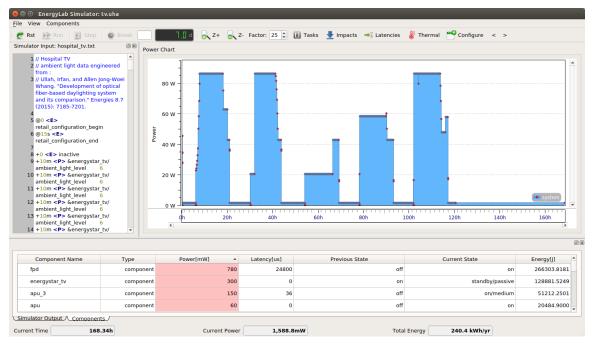

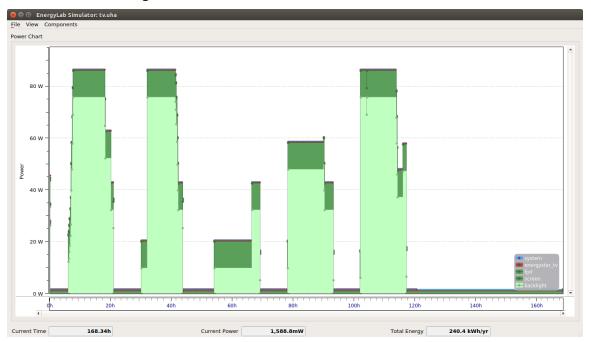

| Figure 15: Power Consumption of the Virtual Prototype Under the Traditional TV Use Case<br>48                        |

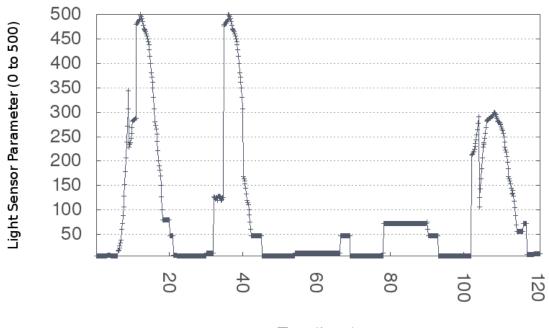

|----------------------------------------------------------------------------------------------------------------------|

| Figure 16: Ambient Light Level in the Traditional TV Use Case                                                        |

| Figure 17: Power Breakdown in the Traditional TV Use Case                                                            |

| Figure 18: Smart TV Use Case                                                                                         |

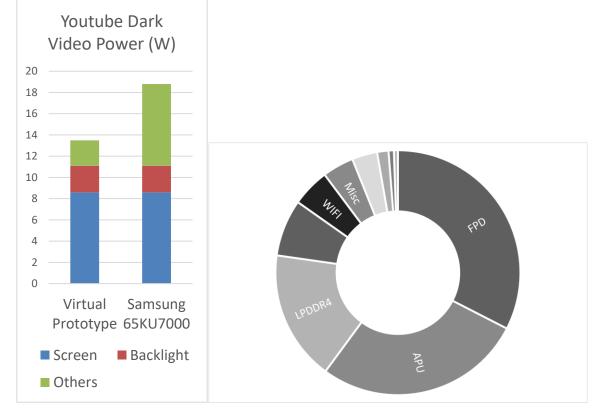

| Figure 19: YouTube App in the Virtual Prototype Compared With the Physical Measurement                               |

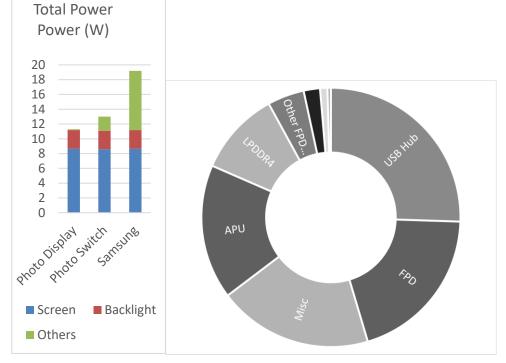

| Figure 20: Power Consumed in the USB Gallery Use Case53                                                              |

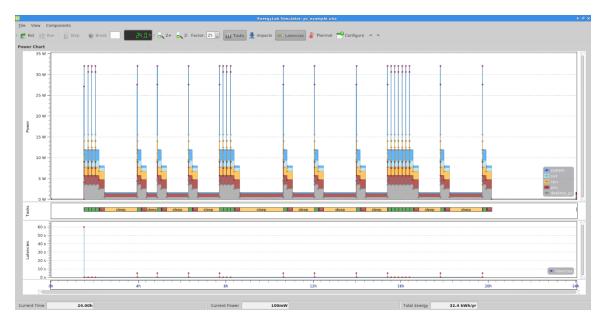

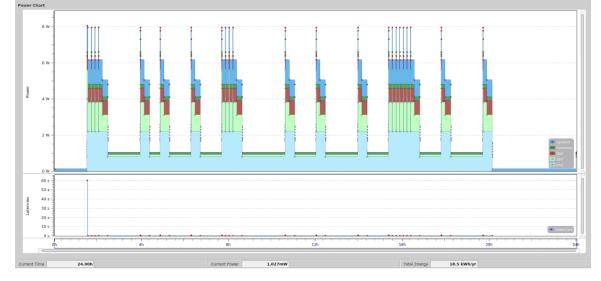

| Figure 21: Power and Latency Graph for a 24-Hour Cycle of the Ideal ENERGY STAR®-PC<br>Model                         |

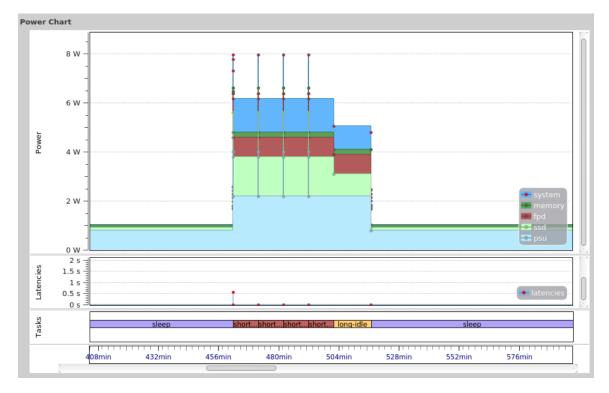

| Figure 22: Power and Latency Graph for a 24-Hour Cycle of the Zynq MPSoC-Based Model 55                              |

| Figure 23: An Enlargement of an Activity Cycle Based on Sporadic User Activity56                                     |

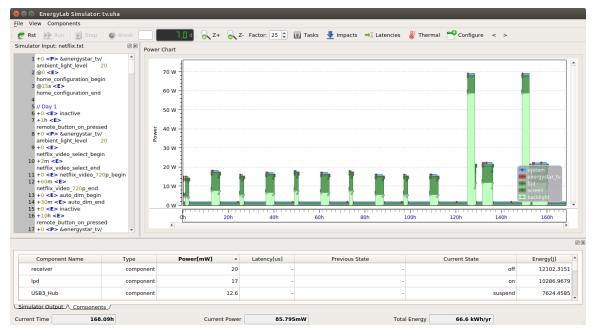

| Figure 24: Feature Demos of the Set-Top Box Virtual Prototype57                                                      |

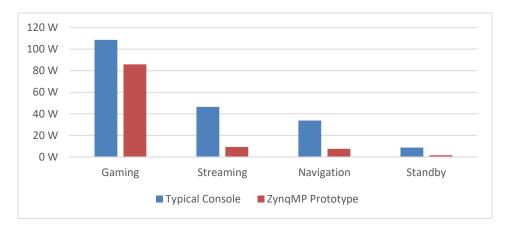

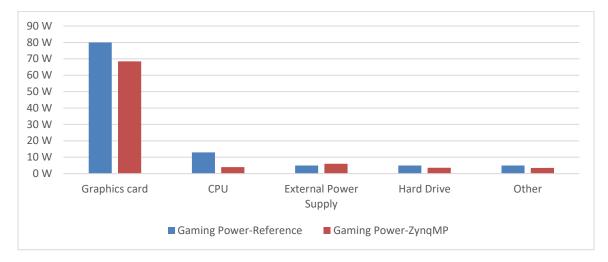

| Figure 25: Power Consumption Comparison Between the Gaming Console Virtual Prototype<br>and a Typical Gaming Console |

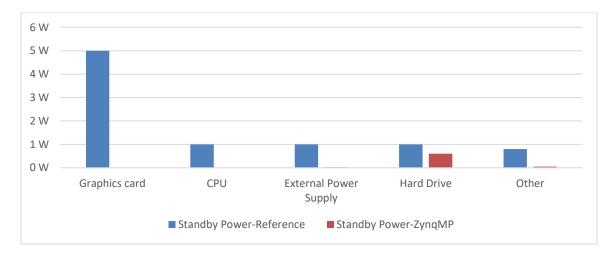

| Figure 26: Per Component Power Savings of the Gaming Console Virtual Prototype in<br>Standby Mode                    |

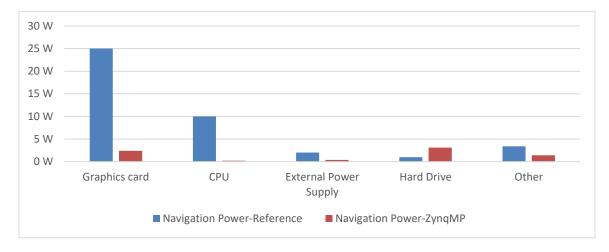

| Figure 27: Per Component Power Savings of the Gaming Console Virtual Prototype in<br>Navigation Mode                 |

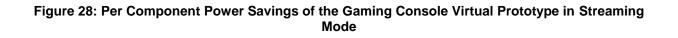

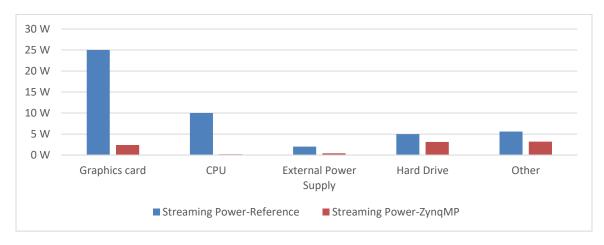

| Figure 28: Per Component Power Savings of the Gaming Console Virtual Prototype in<br>Streaming Mode60                |

| Figure 29: Per Component Power Savings of the Gaming Console Virtual Prototype in<br>Gaming Mode60                   |

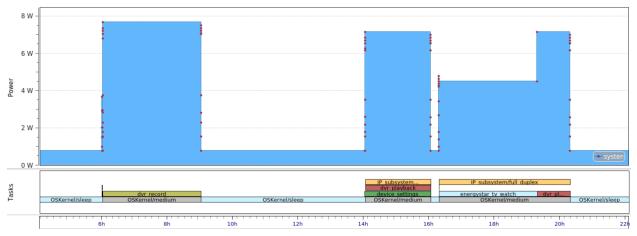

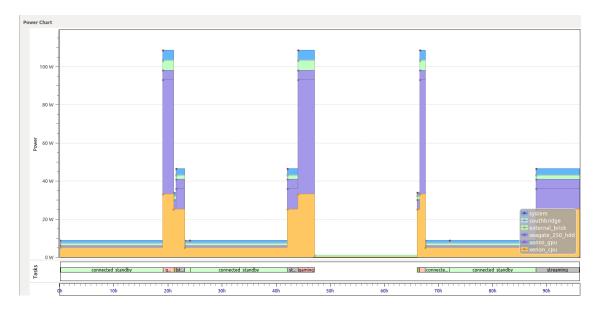

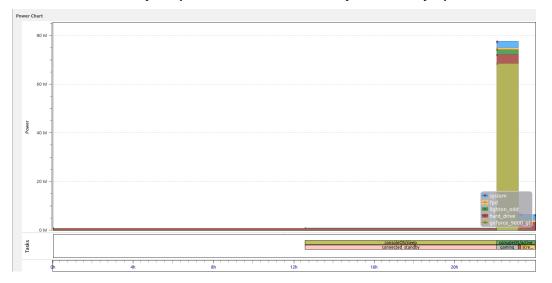

| Figure 30: Power and Latency Graph for a Streaming-Heavy 96-Hour Cycle of the Reference<br>Gaming Console Model      |

| Figure 31: Power and Latency Graph for a Typical 24-Hour Cycle of the Reference Gaming<br>Console Model              |

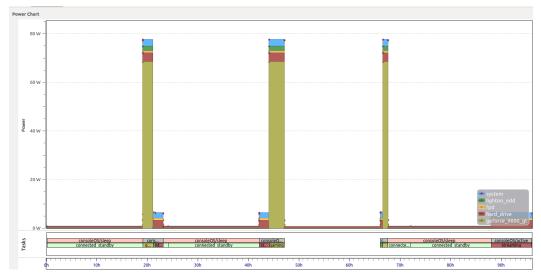

| Figure 32: Power and Latency Graph for a Streaming-Heavy 96-Hour Cycle of the Zynq<br>MPSoC-Based Model              |

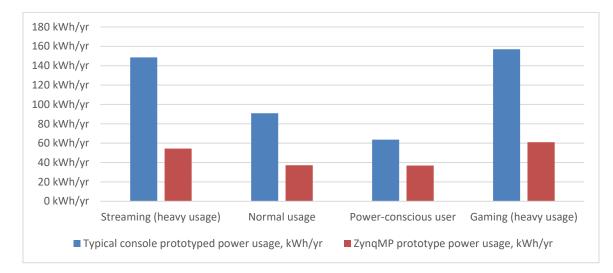

| Figure 33: Yearly Power Usage of the Gaming Console Virtual Prototype63                                              |

| Figure 34: Power and Latency Graph for a Normal 24-Hour Cycle of the Zynq MPSoC-Based<br>Model                       |

| Figure 35: Architecture Diagram of the Set-Top Box Reference Design                                                  |

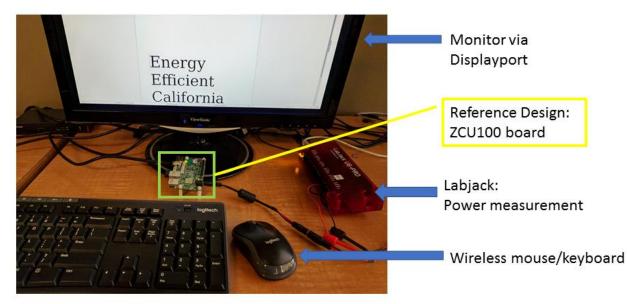

| Figure 36: Reference Design Testing Set-up70                                                                         |

|----------------------------------------------------------------------------------------------------------------------|

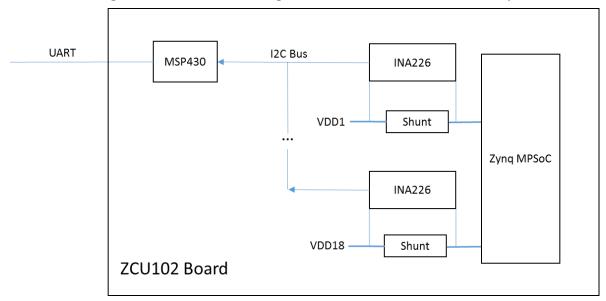

| Figure 37: Measurement Diagram of ZCU102 Rail Measurement System                                                     |

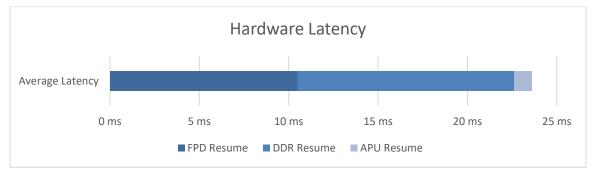

| Figure 39: Hardware Latency Breakdown by Component: Full-Power Domain, DDR SDRAM,<br>and Application Processing Unit |

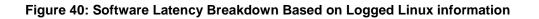

| Figure 40: Software Latency Breakdown Based on Logged Linux information77                                            |

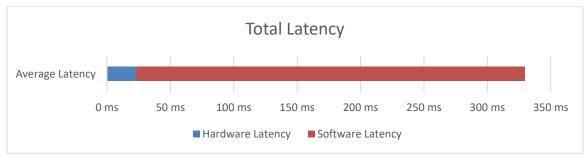

| Figure 41: Total Latency Breakdown Into Hardware and Software Latency                                                |

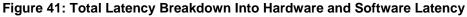

| Figure 42: USB Gallery: Power Consumption With Standard Deviation                                                    |

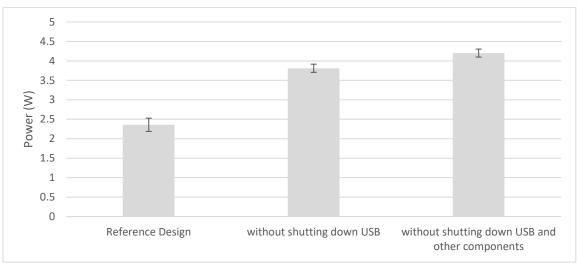

| Figure 43: Power Consumption of the Reference Design Compared With a Traditional PC81                                |

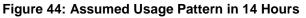

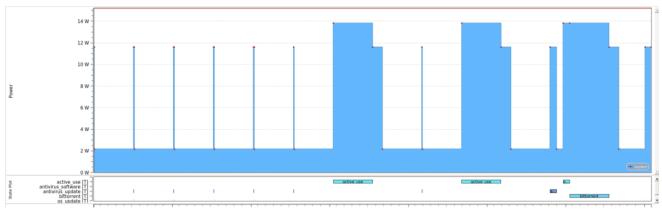

| Figure 44: Assumed Usage Pattern in 14 Hours82                                                                       |

| Figure 45: Power Comparison Average to a Year82                                                                      |

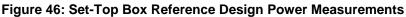

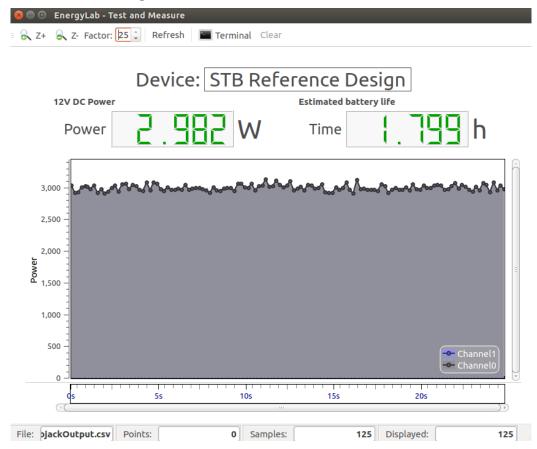

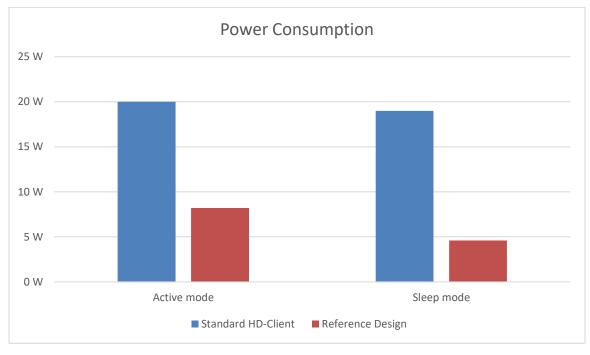

| Figure 46: Set-Top Box Reference Design Power Measurements83                                                         |

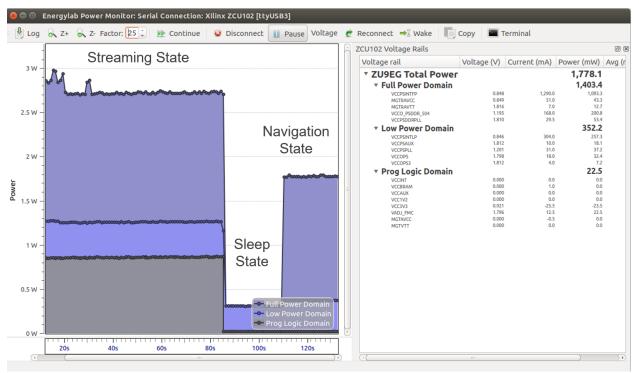

| Figure 47: DC Power Measurement of ZCU10084                                                                          |

| Figure 48: Comparison of Reference Design and the Baseline                                                           |

| Figure 49: Comparison of Reference Design to Traditional Console                                                     |

# LIST OF TABLES

| Table 1: Resulting System Power Consumption                                             |

|-----------------------------------------------------------------------------------------|

| Table 2: States in TV High-Level Modeling                                               |

| Table 3: Power States of the Flash Chip    27                                           |

| Table 4: ULPI Power States    29                                                        |

| Table 5: Wi-Fi Receiver States    30                                                    |

| Table 6: Wi-Fi Transmitter States                                                       |

| Table 7: States of the Amplifier Driving the Speaker                                    |

| Table 8: Power Models of the HDMI Host                                                  |

| Table 9: Comparisons With the Samsung TV, Excluding the Screen and the Back Light       |

| Table 10: Expected Power Savings From the Gaming Console Virtual Prototype           58 |

| Table 11: Power Savings of the Gaming Console Virtual Prototype                         |

| Table 12: Power Consumption and Savings of Computer Reference Design                    |

| Table 13: Breakdown of Power Consumption by Component | 84 |

|-------------------------------------------------------|----|

| Table 14: Set-Top Box Power and Energy Savings        | 85 |

| Table 15: Gaming ConsolePower and Energy Savings      | 87 |

# **EXECUTIVE SUMMARY**

# Introduction

Market leaders in mobile products, like California-based Apple<sup>®</sup>, have developed batterypowered electronic devices with highly sophisticated functionality and minimal energy consumption. The intriguing question is how the best design practices from the mobile industry leaders, like Apple, can be applied to improve the energy efficiency of plug-load devices like TVs, computers, game consoles and set-top boxes. Lower energy consumption of plug loads leads to increased building energy efficiency and is essential to reach California's ambitious energy efficiency goals.

Energy management of plug-load devices is either provided as part of the proprietary hardware and software integrated in the device by in-house power design teams or is controlled externally through independently supplied add-on devices that cut off the power supply (e.g. advanced power strips). Whereas the former approach comes with high costs for specialized components, software, and design know-how, the latter is prohibitive due to long recovery times for the device after the power is restored, which results in long wake-up latencies not tolerated by the users.

Apple and other mobile market leaders have achieved extraordinary results in mobile energy efficiency and even ported their mobile efficiency principles to wall-powered device design. However, the vast majority of other plug-load devices are designed by outsourcing companies that are not skilled in energy efficiency technologies. This project contributes to the closure of the mobile energy gap by developing design principles, technical standards, virtual prototypes, and reference designs that will enable most plug-load development teams to achieve best-inclass mobile efficiency levels within short time and at low costs.

# **Project Purpose**

This project seeks to reduce the energy consumption of plug-load devices in California's homes and offices by applying mobile design practices. These practices include the adoption of the energy proportionality principle, selection of energy- and cost-efficient hardware components, and implementation of specialized energy management software kernels that monitor and control device power. Based on these innovations, the objective is to develop, tune, and deploy best practice guidelines in form of methodology documents and reference designs for energyefficient plug-load designs to the manufacturers of plug-load devices and their hardware suppliers, software suppliers, and regulators.

The centerpiece of the project is the development, formal standardization, and industrywide deployment of the technical standard for energy proportional computing called *Unified Hardware Abstraction and Layer for Energy Proportional Electronic Systems*. The proposal of the new standard is submitted to the IEEE P2415 Working Group and is supposed to be adopted by IEEE by the end of 2020. IEEE P2415 defines the syntax and semantics for energy-oriented description of hardware, software and power management for electronic systems. It enables

specifying, modeling, verifying, designing, managing, testing, and measuring the energy features of the device, covering the pre- and postsilicon design flow.

### **Project Process**

The main approach to achieving energy savings in plug-load devices is to follow the *energy-first design principle*. The longer development engineers postpone tuning the power aspects of the devices, the more difficult it becomes to alleviate inefficiencies, resulting either in increased cost or in less optimal energy efficiency. So, rather than implementing functionality first and tuning power once the functionality is complete, the project approach is to take energy into account at every step of development.

The first step is to do energy modeling using virtual prototypes. An energy-oriented virtual prototype allows simulation of the power states of the complete device for a set of use cases. This kind of simulation provides early insights into the expected energy profile that a device might have for different types of use models. It also allows enhancing optimizing design aspects, and software partitioning which decides how the components of a system are implemented in hardware and which ones in software for energy efficiency.

Once the actual hardware platform becomes available, it is important to continue following the energy-first development method:

- Power measurements should be conducted at all times during all steps of development.

- Software defined energy management principles should be followed.

- Power control should be separated from data processing.

- Power control and monitoring should be delegated to a dedicated entity in the system.

- Power control interfaces should be abstracted to allow different software layers to issue power-related requests.

Following these principles, the research team created reference designs for each of the four device types. The reference designs were based on the Xilinx ZCU102 prototyping platform using standard software components that have been extended to include an energy management interface that satisfies the software-defined energy management principles outlined above.

Optimizing energy use in a real device can be daunting, given the complexity of today's systems, both on the hardware side with hundreds of interdependent components, as well as on the software side, with layered software architectures and multiple independent processors running different software applications often developed by different teams. Small changes in the software can often have big impacts on the power consumption of a device.

A crucial factor affecting the ability to optimize the energy behavior of a device is understanding where power is consumed at any given moment. Accurate and fine-grained power measurements are key for gaining this understanding. On the reference designs developed for this project, the research team measured power using measurement circuitry that is embedded on the development board used, providing detailed visibility into the power consumption of individual voltage rails.

Using the detailed visibility of power consumption on the real device with the knowledge gained on the virtual platforms, opportunities for energy efficiency optimizations were easily seized. This ensured that in any given application state, each hardware component of the system was in the lowest possible power state, satisfying functional and latency requirements of the respective application.

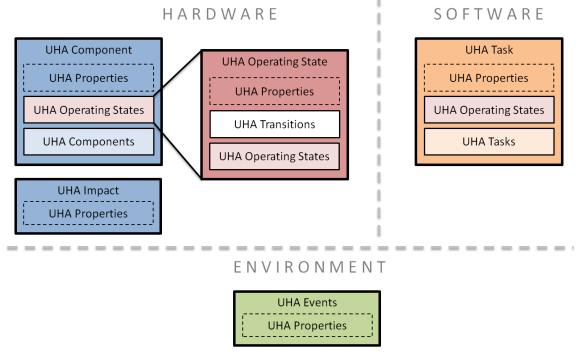

Throughout this project, the design method has been refined and extended, while the unified hardware description, which is a standardized language, was used to model electronic systems. This format was tested by applying it to the different designs and at different levels of abstraction which is the process of removing physical, and spatial details to study the attributes of an electronic system. A key objective was to produce a description format for energy models that meets the needs of software and system developers, including expressive power and readability, while allowing reuse of models as well as collaboration between teams. Reuse is especially important since a system designer will want to source the energy models from their IP and chip vendors rather than describing all components from the ground up themselves.

Ultimately, the work done during this project helped produce the current version of the unified hardware description, which has been submitted to the IEEE P2415 working group for standardization.

#### **Project Results**

Using the proposed method, the team created virtual prototypes of each device and has implemented reference designs based on a commercially available development board. For each device that has been targeted, the final reference designs demonstrated significant energy savings compared to the typical devices.

Effective energy modeling and virtual prototyping require a suitable description format to capture the energy-related behavior of a system and complete device. For this purpose, the unified hardware abstraction layer has been refined and extended based on the experience gained throughout this project, culminating in the donation of the layer to the IEEE P2415 working group. The IEEE standardization efforts are a key factor in enabling wider adoption of the design method proposed in this project. The design method provides industrywide agreement on a description format, promoting information exchange and reuse of models across teams and between suppliers and system integrators. The electronic design tools produced by industry increase the versatility of the energy models, similar to how the language standards from the 1980s standardized how functional aspects of hardware were described, giving birth to a multibillion-dollar design automation industry.

# **Technology** Transfer

One part of the technology transfer effort was to standardized the unified hardware abstraction through the IEEE standardization body. The status of the standardization is that a final proposal has been submitted to the P2415 working group. To promote the developed technology in front of the industry, the findings from this project have been presented at several forums.On February 8, 2018, AGGIOS was invited by NRDC to present the findings from the Electric Program Investment Charge (EPIC) mobile efficiency project to the set-top box community during their STB voluntary agreement meeting in Denver. On August 15, 2018, AGGIOS held an emerging technologies webinar hosted by the California Energy Commission to present the results of the EPIC project to a wide audience from the industry as well as regulators. The webinar had more than 140 attendees.

# **Benefits to California**

Considering the large numbers of TVs, set-top boxes, computers, gaming consoles, and other plug-load devices, the energy use in California can be reduced significantly if the energy-first design method developed in this project is adopted by industry.

This research does not provide increased ratepayer reliability or safety; however, it can lower customer electric bills, and can add to a significant contribution to California's statutory greenhouse gas reductions and energy efficiency goals. At a large scale, this project holds the potential for long-term, deep savings across a broad array of plug-load devices.

Consistent deployment of the new technology has the potential to reduce the annual energy consumption of targeted electronic plug-load devices in California homes and offices by 20-50 percent and achieve statewide cumulative savings through 2022 of 1.6–4 terawatt-hours (TWh), depending on the range of addressable products and depth of per-unit savings. (A terawatt is one trillion watts.)

This project will additionally accelerate the use of mobile efficiency technologies across product categories by influencing policy mechanisms to accelerate adoption of mobile efficiency technologies. These policy pathways include:

**California Title 20:** The results and implementation of this work can enable the Energy Commission to revise energy allowance values downward resulting in significant savings relative to today's proposed levels.

**Voluntary Agreements:** Results from this project can be used to renegotiate voluntary agreements or influence the stringency of future tiers of electronic standards.

**ENERGY STAR®:** As mobile efficient wall-powered devices begin to appear in the market, ENERGY STAR can set appropriate allowance levels to accelerate the adoption of mobile efficiency technology in wall-powered devices. ENERGY STAR can also list the future Unified Hardware Abstraction IEEE P2415 electronic standard compliance as a requirement to support this industrywide standards effort.

**Utility Incentive Programs:** Utility program s can use incentives to accelerate the adoption of ENERGY STAR products based on mobile efficiency.

# CHAPTER 1: Overview

Miscellaneous plug loads constitute a significant portion of the energy consumption in California's households. The capabilities of many of these devices are converging as they often are built on top of similar platforms. This project focuses on the energy efficiency of personal computers, gaming consoles, TVs as well as set-top-boxes. While each of these devices has a unique functionality, the devices have a large set of common capabilities. Those same capabilities are also offered by many mobile devices, which often have similar processing power but consume far less energy.

This project explores and quantifies how an improved development method can help improve the energy efficiency of these plug-load devices.

# CHAPTER 2: Method

When it comes to mobile devices, the industry has already understood that energy efficiency is most effectively achieved when including it as a key criterion early in the design process, producing remarkable results in terms of energy efficiency without sacrificing performance. Cost is often cited as a reason why traditional plug-load devices ignore energy efficiency. This project aims to demonstrate that when using the right method, energy efficiency can be achieved without significantly increasing development costs.

This chapter describes the method used for developing energy-efficient devices throughout this project. It consists of an energy-first development process starting with virtual prototypes, followed by using software-defined energy management principles on the final device alongside detailed power measurements throughout development.

# **Energy-First Development**

Most plug-load devices are being developed with a focus on functionality and performance. Energy efficiency either is often neglected entirely or is introduced in the late stage of product development. Consequently, power savings are often difficult to achieve without requiring a redesign of parts of the hardware and software that has already been finalized, resulting in substandard energy efficiency.

The energy-first development process that has been applied throughout this project starts with modeling and simulation, followed by constant measurement and monitoring of power consumption during the implementation phase.

# Power Modeling Using Unified Hardware Abstraction

To create suitable models of the energy behavior of the devices in question, the research team used the Unified Hardware Abstraction (UHA) language. UHA descriptions consist of

- Models of hardware components and related power states.

- Models of software and external events.

- Dependencies between the software and components.

By modeling the power states of components, as well as the dependencies between the components and the dependencies between software and the hardware, the power consumption of the overall system can be accurately estimated.

# **UHA Language Elements**

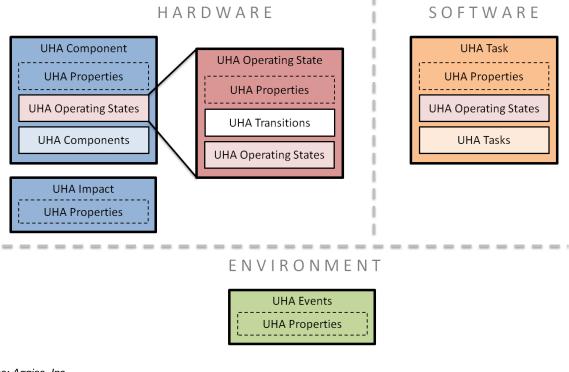

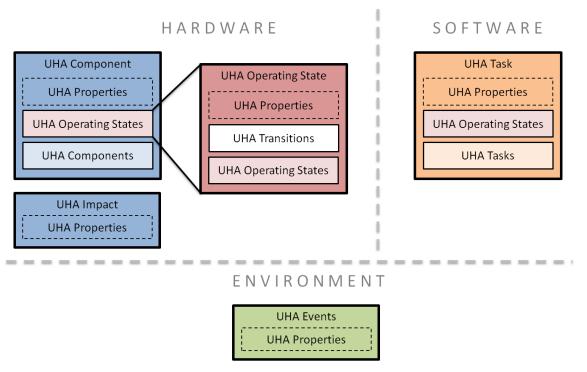

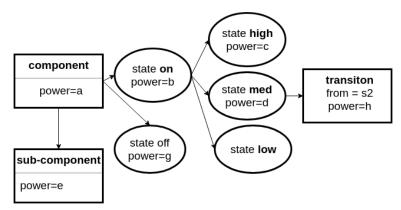

The main language elements of UHA are objects and properties. UHA objects describe objects such as components, software tasks, or power states such as on and off. UHA properties describe attributes of an object.

#### Figure 1: UHA Objects and Properties

Source: Aggios, Inc.

The syntax of UHA is based on the device tree syntax. references (Linaro Limited, 2016): (<u>https://elinux.org/Device\_Tree\_Reference</u>; <u>https://www.nxp.com/docs/en/application-note/AN5125.pdf</u>).

Beyond the device tree syntax, UHA has support for annotating object types and run-time parameters, as well as support for arithmetic expressions and lookup tables.

### **Modeling Hardware Components and Power States**

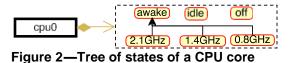

Hardware components are modeled as UHA objects. Hardware components can be hierarchical; in other words, a hardware component can have subcomponents. A special type of UHA object is the power state, or UHA state. Each component can have one or more states. States themselves can also be hierarchical.

Each component can have one or more power models as a UHA property. Power models can be specific to a state. Power models can reference properties defined anywhere in the model, that is, component-specific properties or systemwide properties.

UHA transitions are used to describe the behavior of a component when a new state is entered. This includes the related energy profile, as well as the transition latency, i.e. the time it takes to perform the transition from the previous state to the new state. UHA also allows modeling of "control components," i.e. clocks, voltage rails, or reset lines. Control components are an important detail for modeling the power states of digital systems as most power states are controlled by either clocks, voltage rails, or reset lines. Control components typically form hierarchies of their own, such as the clock tree or the voltage hierarchy.

# **Modeling Software and External Events**

In UHA, software is modeled as UHA tasks, while the influence of hardware events is modeled as UHA impacts. UHA tasks and impacts may be hierarchical and they may have states. (E.g., an operating system task is active or in a suspended state.) Software states are important in determining overall transition latencies as those latencies may be the gating factor for being able to enter low power states during periods of inactivity.

# **Modeling Dependencies**

Dependencies are a crucial aspect of UHA models, ensuring that only valid combinations of states are being considered when simulating the energy-related behavior of a system.

UHA dependencies for software tasks describe the needs of a software task with respect to states of hardware components. UHA dependencies also extend to relationships between hardware components, specifically between the states of components.

### **Explicit Dependencies**

Dependencies can be expressed explicitly using the "requires" property.

```

cpu {

state on {

requires = &bus/active;

}

}

```

The above example shows a simple explicit dependency between two hardware components. It specifies that for the "cpu" component to be in the "on" state, the "bus" component must be in the "active" state.

More complex dependencies can be expressed as well, such as the requirement on a specific set of capabilities, or numeric requirements, for example, on a quality of service capability or a certain memory throughput capacity. Dependencies on latencies can be expressed as well.

#### **Control Dependencies**

Control dependencies are established by identifying the respective control parent(s) of a component and then describing the required state of the control parents for a given state of the component. Control dependencies are especially important when one or more components share the same clock or the same voltage rail, effectively linking the power states of several components despite those components potentially being functionally independent.

Control dependencies can also refer to clock frequencies or voltage levels rather than just states.

### **Modeling Latencies**

Modeling latencies in UHA serve two purposes. On one hand, latencies capture the delays incurred when state transitions are performed, which allows tools to report and analyze such latencies. On the other hand, UHA also allows expressing dependencies in terms of latency requirements.

Latencies are modeled in UHA by defining state transition latencies for each component in the hierarchy. The transition latencies captured for one component shall account only for the time it takes for the component to transition from the previous state to the new state—they should not include the latency of other state changes triggered by any of the components requirements, such as changing of a clock frequency or turning on a clock or voltage source.

The total latency for the state transition of a components can be computed by aggregating the latency of the state transition with the latencies of all state transitions resulting from the dependencies.

### **Defining Entry and Exit Latency Properties**

A UHA state may define entry and exit latency properties. The *transition latency* is computed by adding the exit latency of the old state or source state and the entry latency of the new state or target state.

```

eth0 {

state on {

entry-latency = 8ms;

}

state idle { }

state off {

exit-latency = 5ms;

}

}

```

The code above describes a component with the respective transition latencies. The total latency for entering the on state is either 8 millisecond (ms) when transitioning from the idle state or 13 ms when transitioning from the off state.

#### **Defining Latencies Within a Transition**

When transitions are defined explicitly, they may also contain a latency property. This property explicitly specifies the transition latency between pairs of states, i.e., the source and target state.

```

memory {

state on {

transition { // transition from any state

latency = 3ms;

}

transition { // transition from state "off"

from = &off;

latency = 12ms;

}

}

```

In the example above, because the transition from source state "off" is defined explicitly, it supersedes the generic transition specified without a "from" property. Hence, the transition latency into the "on" state is either 12 ms from the off state or 3 ms for all other cases.

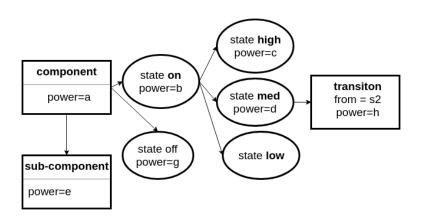

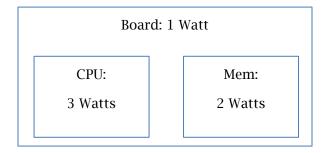

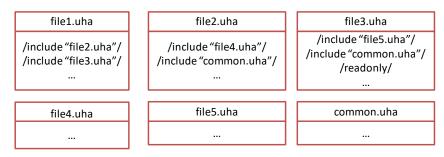

### Power Accounting in UHA

Component power information in UHA is defined on multiple levels. To compute the total power consumption for components and systems, a simple three-step process should be followed.

- The first step is to select a power model for each component.

- The second step is to compute the power for each component.

- The third step is to aggregate the total power of the system or subsystem of interest.

The subsequent sections explain each of the steps in more detail.

#### **Power Model Selection**

Each component shall have only one power model at any instance in time. The rules for selecting the active power model based on the current state are as follows:

Power models specified on the component level are superseded by power models specified in the current state of the component. If no state-specific power model exists for the current state, then the power model defined at the component level is the one that applies.

If there is a hierarchy of states defined, the power model of the leaf state always trumps the power model of the parent(s) state. During a transition, a power model specified in the transition object trumps all other power models for that component.

#### **Power Value Calculation**

For each component, the respective power value is determined using the selected power model and the current values of the referenced properties.

#### **Power Value Aggregation**

The total power is aggregated hierarchically. Hence, for a given component or (sub)system, the total power is computed by adding the power of all children to own power value of the component. Finally, the power values of the active tasks and impacts related to this (sub)system are also added.

For example, to account for the total power consumption of the system, the power values for all the components and related sub-components, the power values of the active segment of the energy profile of the running tasks, and the power values of the active impacts need to be added.

#### Examples

#### **Table 1: Resulting System Power Consumption**

shows an example of a simple model with hierarchical power states and multiple power models. The power accounting and the resulting power consumption for the complete system in different states are in **Error! Reference source not found.**.

The power model for "component" is selected based on the related state, or the transition if the state is in the transition and the transition has the power property defined. Then the total power consumption needs to be added to the power consumption of the associated subcomponent.

#### Figure 2: Power Accounting in UHA Models

Source: Aggios, Inc.

| Component state                 | Total power consumption |

|---------------------------------|-------------------------|

| High                            | c+e                     |

| Med                             | d+e                     |

| Low                             | b+e                     |

| Off                             | g+e                     |

| Transition from "off" to "med"  | h+e                     |

| Transition from "off" to "high" | c+e                     |

#### Table 1: Resulting System Power Consumption

Source: Aggios, Inc.

# **Optimizing Energy Efficiency on the Device**

Once the development shifts to the real device, the method used throughout this project consists of three factors

- Power measurements at every step

- Optimized power management control firmware

- Software defined energy management throughout the software stack

Each of the three factors is equally important when looking to achieve optimized energy efficiency.

#### **Power Measurements**

Probably the easiest and most effective way to ensure energy efficiency is achieved through awareness of the energy profile of a device at all stages of development. Ideally one would have access to highly accurate and granular power data at all times. However, even high-level power measurements using entry-level equipment (e.g. alternating current [AC] power of the entire system) will allow engineers to spot unexpected changes in the energy profile and take corrective action early. Efficiency problems are best fixed at the moment when they're introduced, as it is likely that the responsible software component can be easily identified.

If many software changes are introduced across the system at once, it can be significantly more difficult to isolate the software component that introduced the problem.

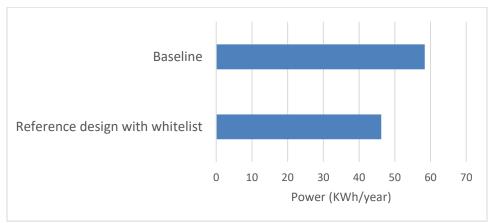

Having the ability to see real-time power data for a device is even more powerful when the power data are broken down by component. In most cases, this is impossible because many components are embedded in a single system on a chip (SoC) and share common voltage rails, which are supplied by the board. Still, when modern SoCs have several independent voltage rails, it is helpful when power measurements are done on a per-rail basis. In the case of the Xilinx ZCU102 board used for this project, there are 18 voltage rails that deliver power to the Xilinx UltraScale+ MPSoC, which is the main SoC of the system. Being able to measure the power consumption of each of these rails makes it easier to associate changes in power consumption to specific components, or at least to small sets of components. This can significantly reduce

the effort required to identify the components that may be to blame for changes in power consumption. This reduction in effort, in turn, reduces the amount of time and effort needed to analyze the power states of those components and ensure that each is in the lowest possible power state given the requirements of the application.

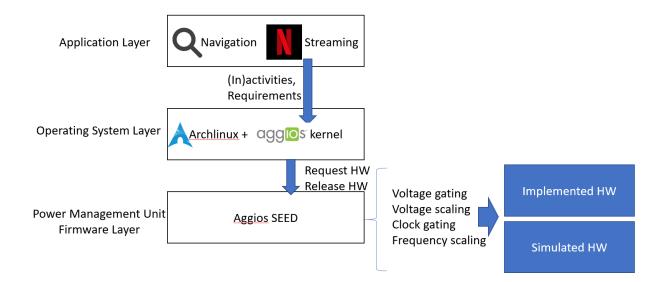

# Software Defined Energy Management

Complex systems used in modern plug loads, such as the devices investigated in this project, usually include more than one operating system, running on more than one heterogeneous set of processors. While the most complex tasks of a given application usually require the most powerful processors to be involved and the main operating system such as Linux to be running, many routine and maintenance tasks can be delegated to smaller processors. However, when multiple software components are running independently of each other and aren't running on top of a single monolithic operating system, it is no longer possible to rely on the big operating system to be in charge of all power management decisions.

Software defined power management is based on the following principles:

- Separation of power control from data processing

- Delegation of power control and monitoring to a dedicated entity in the system

- Abstraction of power control interfaces to allow software to communicate the power state requirements

Applying software defined power management principles to today's plug-load devices requires interfaces across the different layers of the software, including standard operating systems such as Linux.

### **EEMI Interface**

To allow coordination of power management requests across multiple processing units and operating systems an interface is required that follows the software defined power management principles. While standard interfaces for power management exist, they are mostly still targeting a single operating system (United EFI Forum, 2017) (ARM Limited, 2017).

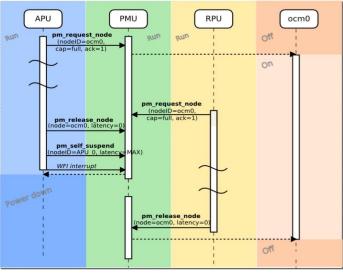

In collaboration with Xilinx, the embedded energy management interface (EEMI) (Xilinx, 2017), has been developed to support the needs of heterogeneous multicore platforms such as the Xilinx UltraScale+ MPSoC (Xilinx, 2017).

### Overview

The EEMI allows software components running across different processing clusters on a chip or device to communicate with a power management controller (PMC) on a device to issue or respond to power management requests.

The EEMI APIs allow one or more processing clusters to manage respective power states, systemwide power states, as well as the power states of slave devices, such as peripherals or memories. EEMI requests are submitted by processing clusters and serviced by the power management controller.

### **Use Cases**

The following basic use cases illustrate the purpose and necessity of the EEMI APIs.

#### Use Case 1: Suspending Linux

When Linux is suspended, the processor it is running on will enter a sleep state. In more complex systems, entering the sleep state of a processor often requires a complex power-down sequence that cannot be safely performed by the affected processor itself.

EEMI offers a "self-suspend" API that tells the power management controller to perform the appropriate sleep-state handling for the affected processing cluster.

#### Use Case 2: Shared Memory

When two processing clusters are using the same memory, then neither entity would be able to safe place that memory into a low-power mode as it isn't aware of the requirements of the other processing cluster with respect to that memory. EEMI includes API functions that allow processing clusters to declare when they need a certain resource and which capabilities they require.

**Error! Reference source not found.** shows the UML diagram including the EEMI API calls for this use case on the Xilinx UltraScale+ MPSoC.

Acronyms used in the UML diagram:

- APU: Application processing unit (Quad-core ARM Cortex A53)

- RPU: Real-time processing unit (Dual-core ARM Cortex R5)

- PMU: Power management unit

- OCM0: On-chip memory bank 0, i.e. the memory being shared

#### Figure 3: UML Diagram for Shared Memory Use Case

Source: Aggios, Inc.

A brief step-by-step description of the use case is outlined below:

Step 1: APU requests OCM0 by calling the pm\_request\_node API, which prompts the power management unit to power on the OCM0 memory bank.

Step 2: RPU also requests OCM0. Since the memory bank is already powered on, no action is required by the PMU.

Step 3: APU releases OCM0 by calling pm\_release\_node. This lets the PMU know that the APU no longer requires OCM0. However, no state change takes place because the PMU knows that the RPU still requires OCM0 to be on.

Step 4: RPU also releases OCM0. Because at this point the RPU was the last remaining user of the memory bank, the PMU will now turn off OCM0.

#### Use Case 3: System Shutdown

System shutdown is another use case that is well understood for simple architectures running a single operating system. However, on a heterogeneous platform with multiple independent software applications, a graceful system shutdown requires a certain degree of coordination. EEMI includes interfaces that enable adequately privileged entities to request a shutdown of a subsystem or the entire system or device. These interfaces inform all processing clusters about the requested system shutdown, allowing them to take appropriate measures to gracefully perform the respective shutdown sequences.

### **Optimized Power Management Firmware**

After improving the power behavior of the system using the virtual prototype, UHA power models can also be used to customize the power management firmware for the target. The information contained in a UHA description can include all details necessary to generate the complete power management firmware. However, for the Xilinx UltraScale+ MPSoC that was used for the reference designs, a handwritten firmware already existed so that the UHA description was used to configure the PMU firmware and enable specific optimizations.

Possible optimizations range from lower power states for certain peripherals when those are unused to extended frequency scaling. Applying these optimizations operating systems like Linux typically perform on the main CPUs by lowering the bus frequencies as well as the DDR frequency during periods of low CPU frequency. Due to the already low energy consumption of ARM CPUs, pure CPU frequency scaling shows little noticeable benefit when no load is applied, whereas scaling of bus and memory frequencies can increase the savings by more than an order of magnitude.

# CHAPTER 3: Virtual Prototypes

Today, many product development teams for plug-load devices concentrate on functionalities first, measure the power consumption of the system only after they have a first physical implementation, and then try to enhance power consumption if the measured power is undesirable. At this stage in development, it is often impractical to make significant changes to the hardware or software design due to engineering difficulties or product timeline constraints. Therefore, many products are released with barely minimum power optimization to cover the heat dissipation needs.

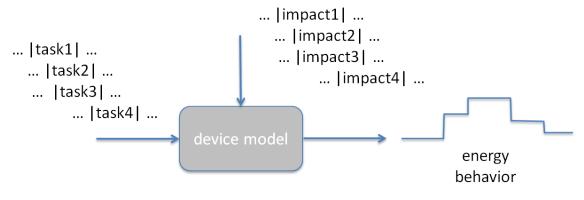

The use of virtual prototyping is one of the critical design principles advocated that addresses this problem. Virtual prototyping is a design method that models the target system using power modeling tools at a very early stage, typically before the hardware is designed. The modeling involves the hardware and the software, targeting at typical usage scenarios.

The virtual prototype can be organized as two stages. In the first stage, in the high-level modeling stage, device models are built by modeling the high-level components. The power models are derived from the measurements of similar devices, from estimates based on the engineer's experiences or from regulatory requirements. The high-level modeling gives an estimated bound of the power consumption and provides reasonable expectations on the power consumptions of the final product. In the second stage, detailed virtual prototyping shall be conducted with the information on:

- 1. Power models on specific components. The high-level components should be split down to subcomponents with the detail that allows accurate modeling of the power, latency, and dependency with other components.

- 2. Latency modeling on specific components. Most plug-load devices will benefit from power optimizing algorithms with latency considerations. For example, if all components of a device have a very short latency when switched from the off state to the active state, the device has the potential to be put in the off state in short periods when the user is not using the device.

- 3. User behavior modeling. The way the user uses the device has enormous effects on the power consumption of the device.

- 4. Dependency modeling. In many cases, merely modeling the components of the device is not sufficient to derive an accurate power and latency model of the system. Many components have dependencies for it to operate correctly. For example, a hard drive on a gaming console has dependencies on the SATA controller in the system, either on the motherboard or as part of the system-on-chip (SoC). The SATA controller, in turn, has dependencies on the respective power network and clock network. If one were to

consider only the power consumption of the hard drive itself without accounting for these dependencies, it would be an underestimate.

The high-level modeling and the detailed modeling are optional. For some devices, the highlevel modeling is sufficient—for example, when the device is modified from an existing device with a small number of changes, or the lack of information makes the detailed modeling too expensive. For other devices, the high-level modeling is unnecessary when there is already enough information to conduct detailed modeling.

The simulations of all the virtual prototypes in this chapter is performed with EnergyLab Version 0.2.001.

# **High-Level Modeling**

The research team conducted high-level modeling on the targeted plug-load devices for several purposes. The first goal was to demonstrate how ENERGY STAR®-compliant devices operate under the standard test procedures defined in the ENERGY STAR standard. Second, the devices were split into high-level subsystems to pinpoint those subsystems that consume a significant amount of power or the subsystem with the most promising power savings potential.

# Set-Top Box High-Level Modeling

The high-level model of the set-top box captures the ENERGY STAR®-typical energy consumption (TEC) budgets and adders (EnergyStar, 2014), along with the TEC power states and design choices for the various features that a set-top-box device may include.

The model has to capture:

- The power states of the device.

- TV\_watch, i.e. the active state.

- Sleep, i.e. the basic inactive state.

- APD, i.e. the auto-power-down state.

- Sched\_sleep, i.e. the scheduled sleep state.

- The TEC base allowance corresponding to the different types of devices covered by the ENERGY STAR standard.

- The TEC adders corresponding to the different features a set-top box device may have.

- The assumed daily distribution of device states making up the TEC allowance.

#### **Modeling Power States**

Each power state defined in the ENERGY STAR®-specification is represented by a UHA state.

```

state active {

power = TBD;

```

```

transition {

from = &sleep;

latency = 15s;

}

transition {

from = &deepsleep;

latency = 15s;

}

```

As the power levels are not prescribed by the ENERGY STAR<sup>®</sup>-specification, the power levels are left undefined using the "TBD (To Be Determined)" construct.

The transition latencies from the other power states are specified explicitly inside UHA transitions.

Even without explicitly defined power levels, it is possible to express relationships between power levels of different states using assertions.

Maximum allowed power levels for a particular state for example are described as in the following example:

```

state sched_sleep {

power = TBD;

maxpower = &active/power_max*0.15;

assert = <power LE maxpower>;

assert = <power LE 3W>;

}

```

Furthermore, for each state a corresponding task has been defined that represents the requirements for a particular device state.

#### Modeling TEC Power Allowances

The TEC base allowance is described by defining the different types of devices and then asserting that only one of them may be instantiated:

```

device {

requires = &cable/present XOR

&sat/present XOR

&mvpd/present XOR ...

cable {

state present { power = 50kWh / 365 / 24h; }

state ignore { power = 0; }

}

}

```

Using the "requires" property as well as the XOR operator, one can assert that exactly one of the listed devices must be present.

Each device has an associated TEC base allowance defined using the power model in the "present" state.

The TEC adders defined in the ENERGY STAR<sup>®</sup>-specification are described as UHA components. As ENERGY STAR<sup>®</sup>-does not prescribe power levels by power state for those additional features, the entire the TEC adder figure is converted to a power number for the component.

Requirements and assertions are used to express the dependencies or mutual exclusions for sets of features, such as in the case of the DOCSIS (CableLabs, 2017) support:

```

docsis {

requires = &docsis0/present XOR

&docsis2/present XOR

&docsis3/present;

docsis0 {

state present { power = 0; }

}

docsis2 {

state present { power = 25kW / 365 / 24; }

```

```

state ignore { power = 0; }

}

docsis3 {

state present { power = 45kW / 365 / 24; }

state ignore { power = 0; }

}

```

#### Modeling the TEC State Profiles

The ENERGY STAR<sup>®</sup>-specification defines specific state profiles that are to be used to determine the energy consumption of a particular device. These state profiles are expressed using tasks with activity profiles.

```

task with schedsleep {

t_sched = parameter {

default = 2h;

min = 0;

max = 4h;

}

TEC = activtity-profile {

{

requires = tv_watch;

length = 14h;

},

{

requires = tv sleep;

length = 10h - t_sched;

},

{

requires = tv_schedsleep;

length = t_sched;

```

```

}

iterations = 365;

}

```

The example above shows the state profile for devices with a scheduled sleep state. The UHA activity profile shown includes three segments, one for each of the states, along with the expected duration. In this case, the duration of the sleep and schedsleep segements depends on the configuration parameter "t\_sched," which defaults to 2 hours.

#### PC High-Level Modeling

#### **Modeling the Power States**

Each power state defined in the ENERGY STAR<sup>®</sup>-specification is represented by a UHA state.

```

state active {

power = TBD;

transition {

from = &sleep;

latency = 5s;

}

transition {

from = &off;

latency = 60s;

}

}

```

As the power levels are not prescribed by the ENERGY STAR<sup>®</sup>-specification, the power levels are left undefined using the "TBD" construct.

The transition latencies from the other power states are specified explicitly inside UHA transitions.

Even without explicitly defined power levels, it is possible to express relationships between power levels of different states using assertions.

Maximum allowed power levels for a particular state are described as in the following example:

```

state sleep {

requires = &memory/context;

power = TBD;

max_power = max_sleep_power + 0.03 * C;

assert = <power LE max_power>;

}

```

Furthermore, for each state, a corresponding task has been defined that represents the requirement for a particular device state.

#### Modeling the TEC Base Allowance

The TEC base allowance is described by defining the different types of devices and then asserting that only one of them may be instantiated:

```

device {

requires = &pc_ES250/present XOR

&pc_ES425/present XOR

&pc_ES690/present XOR

&notebook/present;

pc_ES250 {

description = "Computer with ES <= 250";

state present { power = 50kW / 365 / 24; }

state ignore { power = 0; }

}

}</pre>

```

Using the "requires" property as well as the XOR operator, one can assert that exactly one of the listed devices must be present.

Each device has a TEC base allowance defined using the associated power model in the "present" state.

#### Modeling the TEC Adders

The TEC adders defined in the ENERGY STAR specification are described as UHA components. As ENERGY STAR<sup>®</sup>-does not prescribe power levels by power state for those additional features, the entire TEC adder figure is converted to a power number for the component.

# **TV High-Level Modeling**

The TV high-level model is engineered based on Samsung UN65KU7000F (Samsung Electronics, 2016).

The states the research team modeled for the ENERGY STAR-certified TV includes all the states mentioned in the ENERGY STAR<sup>®</sup>-specification. These states and associated dependencies are in the table below.

| State                        | Dependencies                           | Description                                                                                                                                                                                                    |

|------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On                           | Screen on, CPU and other components on | The TV is connected to the main<br>power and is capable of producing<br>dynamic video.                                                                                                                         |

| Passive Standby              | Screen off, CPU in S1 state            | The TV is inactive and can be<br>switched into another mode with<br>only the remote-control unit or an<br>internal signal.                                                                                     |

| Active Standby / Low         | Screen off                             | The TV is inactive, can be switched<br>into another mode with the remote-<br>control unit or an internal signal, and<br>can be switched into another mode<br>with an external signal.                          |

| Active Standby / High        | Screen off                             | The TV is inactive but is<br>exchanging/receiving data with/from<br>an external source and can be<br>switched into another mode with the<br>remote-control unit, an internal<br>signal, or an external signal. |

| Download Acquisition<br>Mode | Screen off, Ethernet on                | The TV is inactive but is downloading data from the network                                                                                                                                                    |

| Off                          | N.A.                                   | The TV is switched off.                                                                                                                                                                                        |

#### Table 2: States in TV High-Level Modeling

Source: Aggios, Inc.

The details of the model are not listed here due to space considerations. The most critical observation from this high-level modeling is the state of the screen is essential in determining the state of the TV. This observation is not surprising because when the user looks at an active screen, the user always perceives that TV is active. This fact indicates a potential opportunity for power savings because it is possible to keep the screen active while keeping other components in an inactive mode periodically for power conservations.

# Gaming Console High-Level Modeling

For AGGIOS' game console prototype, the research team conducted a high-level modeling effort based on the power behaviors of Microsoft's<sup>®</sup> Xbox 360 (Microsoft, 2013). While the Xbox 1 is current as of this writing, detailed researches on the internals of Xbox 1 are unavailable from open sources at the time of the study; so the 360 was chosen as the device source.

Statistics on the power behavior of the Xbox 360's is obtained from the National Resource Defense Council's 2014 report (Delforge & Horowitz, 2014), funded by a grant from the U.S. Environmental Protection Agency. Testing was conducted by Pierre Delforge, an NRDC researcher working on electricity consumption in the IT and consumer electronics sectors and the former lead energy and climate strategist for Hewlett-Packard's sustainability group. The protocols used for NRDC's tests are described in the AGGIOS did no separate testing of different 360 models.

# Subsystem Energy Modeling

With the power profile derived from the high-level modeling performed earlier, the research team modeled the proposed virtual prototypes. The detailed modeling gives the engineers opportunities to experiment on different hardware options before developers of a plug-load device build the hardware; therefore, the modeling allows the engineers to make compromises between power and other design factors, such as performance, cost, and form factor.

# **Modeling Techniques**

It is often impractical to measure directly the power consumption of a component when the component is already soldered on a printed circuit board (PCB) due to the difficulties to inserting shunt registers into the voltage delivery network in an existing PCB. Requiring measuring the power before building a PCB may also be impractical in some cases when the component requires complex logic and auxiliary components to drive it and, therefore, will not enter the desired state when powered individually.

Three techniques have been used to build power/latency models of components: datasheet, black box, and power behavior analysis. For each component, the team chose one of these techniques based on the available data and accessibility of the component.

#### **Modeling From Datasheet**

Some components have published the respective operating states, power consumption, and latency values in the associated data sheets. Sometimes, these values can be used for modeling.

An example for such a model is the USB controller on the ZCU100 board, as shown in **Error! Reference source not found.**

# Figure 4: A Table Listing Typical Power Consumption Values From a USB Controller IC (Microchip, 2017)

|                | Туріс | Typical (mA) |      |

|----------------|-------|--------------|------|

|                | VDD33 | VDD12        | (mW) |

| Reset          | 0.8   | 1.8          | 4.8  |

| No VBUS        | 2.0   | 5.0          | 12.6 |

| Global Suspend | 2.0   | 5.2          | 12.9 |

| 4 FS Ports     | 39    | 35           | 170  |

| 4 HS Ports     | 53    | 42           | 222  |

| 4 SS Ports     | 55    | 683          | 1001 |

| 4 SS/HS Ports  | 93    | 688          | 1132 |

#### TABLE 9-3: DEVICE POWER CONSUMPTION

Source: Aggios, Inc.

In other cases, the data from the datasheet may need to be calibrated before using them for modeling. First, the power or current values given by the datasheet may be a maximum value instead of an average value, as shown in the example in **Error! Reference source not found.**. Second, the data given by the datasheet may contain excessive details. For example, an LPDDR4 component contains 15 states detailing the average current draws for operation details such as burst read and burst write. However, directly using these data is challenging because it requires modeling detailed memory access patents from the application software and system software.

Figure 5: Power Model of N25Q128A

| Parameter                                      | Symbol           | Test Conditions                                                      | Min | Max | Unit |

|------------------------------------------------|------------------|----------------------------------------------------------------------|-----|-----|------|

| Input leakage current                          | ILI              |                                                                      | -   | ±2  | μΑ   |

| Output leakage current                         | ILO              |                                                                      | -   | ±2  | μΑ   |

| Standby current                                | I <sub>CC1</sub> | $S = V_{CC}, V_{IN} = V_{SS} \text{ or } V_{CC}$                     | -   | 100 | μΑ   |

| Deep power-down current                        | I <sub>CC2</sub> | $S = V_{CC}, V_{IN} = V_{SS} \text{ or } V_{CC}$                     | -   | 10  | μΑ   |

| Operating current<br>(fast-read extended I/O)  | I <sub>CC3</sub> | C = 0.1V <sub>CC</sub> /0.9V <sub>CC</sub> at 108 MHz, DQ1<br>= open | -   | 15  | mA   |

|                                                |                  | $C = 0.1V_{CC}/0.9V_{CC} \text{ at 54 MHz, DQ1}$ $= \text{open}$     | -   | 6   | mA   |

| Operating current (fast-read dual I/O)         |                  | C = 0.1V <sub>CC</sub> /0.9V <sub>CC</sub> at 108 MHz                | -   | 18  | mA   |

| Operating current (fast-read quad I/O)         |                  | $C = 0.1V_{CC}/0.9V_{CC}$ at 108 MHz                                 |     | 20  | mA   |

| Operating current (program)                    | I <sub>CC4</sub> | S# = V <sub>CC</sub>                                                 | -   | 20  | mA   |

| Operating current (write status regis-<br>ter) | I <sub>CC5</sub> | S# = V <sub>CC</sub>                                                 | -   | 20  | mA   |

| Operating current (erase)                      | I <sub>CC6</sub> | S# = V <sub>CC</sub>                                                 | -   | 20  | mA   |

Source: Aggios, Inc.

For the first case, it is possible to adjust the power models using measured data. It is often safe to assume that when the component is at the lowest power state, there is only a negligible difference between the power value given from the datasheet and the measured average power.

The reason is simply the power of the lowest state is often very close to zero. In the example in **Error! Reference source not found.**, the maximum power of the lowest state is only 18 microwatts ( $\mu$ W) (10 $\mu$ A current draw from a 1.8 volt [V] voltage supply). Because the total power consumption of the virtual prototype is much higher (100W~200W), directly using this number incurs only a negligible error, which is only 18 $\mu$ W in the worst case. The power models of other states can then be calibrated by measuring the power consumed by the whole board while component is at the desired state, measuring the power consumed by the whole board while the component is at the lowest state, and taking the difference value.

For the second case, it is possible to combine the power consumptions of the detailed states into a smaller number of states by making assumptions on a usage paten, so that many states can be combined into a smaller number of superstates.

## **Modeling by Direct Measurements**

When a component is powered by dedicated power cables, it is sometimes possible to build the power model by direct measurements.

## **Power Behavior Analysis**

In some cases, it is difficult to measure the power consumption of some components. For example, the component may be sharing voltage sources with other components. In these cases, the power model was built by measuring the total power consumption of the television under different usage scenarios and comparing the results by analyzing the usages of different components under these usage scenarios.

## **Power Models of Components**

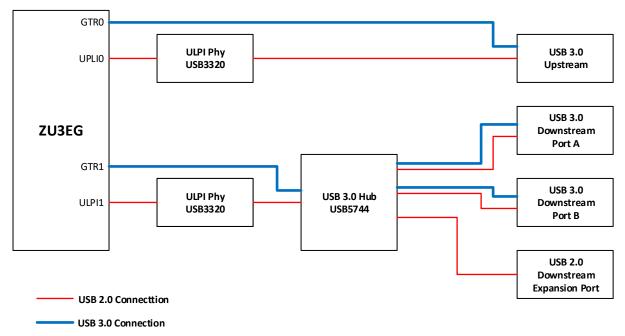

## **Common Components**

All four of the virtual prototypes are modeled based on the ZCU102 platform (Xilinx, 2017). Some components are common. The core of the ZCU102 platform is a system-on-chip (SoC) named Zynq UltraScale+ MPSoC (ZynqMP), which is a heterogeneous multicore SoC containing a powerful quad-core ARM Cortex-A53 suitable for running a complex operating system such as Linux or Windows, a dual-core, real-time processor, a large programmable logic component, or a field programmable gate array (FPGA) The integration of the FPGA provides the research team the ability to implement digital components that are not directly available on the board, e.g., a digital TV tuner that decodes digital TV signals received in an analog format from the physical layer.

## Processors

All four virtual prototypes developed in this project contain software that require processors. For example, in the real world virtually every TV, set-top box, gaming console, and personal computer (PC) relies on an operating system that needs to run on a processor.

The team's virtual prototypes contain processors modeled after the power, performance, and latency behaviors of the SoC, which contains 4 ARM Cortex-A53 (Arm Limited, 2016) cores. The cores use a multilayer cache system that sizes 32/32/1 megabyte (MB).

The power models of these on-chip components were produced with the help from Xilinx, the manufacturer of the SoC.

## Flash

The power profile of the flash memory on the board has been modeled based on the reference manual of the Micron N25Q128A (Micron, 2012) Table 3 outlines the operating modes.

| Mode                                  | Current (Symbol)           | Voltage (V <sub>cc</sub> ) |

|---------------------------------------|----------------------------|----------------------------|

| Standby                               | 100 uA (I <sub>cc1</sub> ) | 1.7V to 2.0V               |

| Deep power-down                       | 10 uA (I <sub>cc2</sub> )  | 1.7V to 2.0V               |

| Operating / fast-read<br>extended I/O | 15 mA (I <sub>cc3</sub> )  | 1.7V to 2.0V               |

| Operating / fast-read dual<br>I/O     | 18 mA (I <sub>cc3</sub> )  | 1.7V to 2.0V               |

| Operating / fast-read quad<br>I/O     | 20 mA (I <sub>cc3</sub> )  | 1.7V to 2.0V               |

| Operating (write status<br>register)  | 20 mA (I <sub>cc5</sub> )  | 1.7V to 2.0V               |

| Operating / erase                     | 20 mA (I <sub>cc6</sub> )  | 1.7V to 2.0V               |

| Table 3: Power States of the Flash Chip | Table 3: | Power | States | of the | Flash Chip | , |

|-----------------------------------------|----------|-------|--------|--------|------------|---|

|-----------------------------------------|----------|-------|--------|--------|------------|---|

Source: Aggios, Inc.

The power-up latency for this chip is 150 us.

## Double Data Rate (DDR)

The DDR chip used in the ZCU100 board is an LPDDR4 module with no documents publicly available. Therefore, the model has been based on the similar MT53B384M64D4 from the same manufacturer (Micron).

The power model of a DDR depends on many operations performed on the DDR. For example, the reading operation from the chip, writing operating to the chip, and keeping the chip in self-refresh without any reading or writing consume different amounts of current from the three voltage sources. However, directly using the models with such an excessive amount of details will require modeling the detailed behavior of the memory access patterns of the software, which is typically impractical.